11-Beta hydroxysteroid dehydrogenase

A low-dropout or LDO regulator is a DC linear voltage regulator which can operate with a very small input–output differential voltage.[1] The advantages of a low dropout voltage include a lower minimum operating voltage, higher efficiency operation and lower heat dissipation.[2]

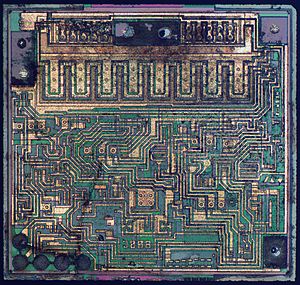

The main components are a power FET and a differential amplifier (error amplifier). One input of the differential amplifier monitors the fraction of the output determined by the resistor ratio of R1 and R2. The second input to the differential amplifier is from a stable voltage reference (bandgap reference). If the output voltage rises too high relative to the reference voltage, the drive to the power FET changes to maintain a constant output voltage.

For the circuit given in the figure the output voltage is given as

Overview

The adjustable low-dropout regulator debuted on April 12, 1977 in an Electronic Design article entitled "Break Loose from Fixed IC Regulators". The article was written by Robert Dobkin, an IC designer then working for National Semiconductor. Because of this, National Semiconductor claims the title of "LDO inventor".[3] Dobkin later left National in 1981 and founded Linear Technology where he is currently chief technology officer.[4]

Regulation

Low-dropout (LDO) regulators work in the same way as all linear voltage regulators. The main difference between LDO and non-LDO regulators is their schematic topology. Instead of an emitter follower topology, low-dropout regulators utilize open collector or open drain topology. This enables transistor saturation, which allows the voltage drop from the unregulated voltage to the regulated voltage to be as low as the saturation voltage across the transistor.

If a bipolar transistor is used, as opposed to a field-effect transistor or JFET, significant additional power may be lost to control it, whereas non-LDO regulators take that power from voltage drop itself. For high voltages under very low In-Out difference there will be significant power loss in the control circuit.[5]

Because the power control element functions as an inverter, another inverting amplifier is required to control it, which increases schematic complexity compared to simple voltage stabilizer.Potter or Ceramic Artist Truman Bedell from Rexton, has interests which include ceramics, best property developers in singapore developers in singapore and scrabble. Was especially enthused after visiting Alejandro de Humboldt National Park.

Power FETs may be preferable to reduce power consumption, but this poses problems when the regulator is used for low input voltage, as FETs usually require 5 to 10V to close completely. Power FETs may also increase the cost.

Efficiency and Heat Dissipation

One of the advantages of having a low drop-out voltage is the ability to limit power dissipation and achieve higher efficiency. The power dissipated by a typical LDO is calculated as follows:

Therefore, one can calculate the efficiency as follows:

Template:Spaces where Template:Spaces

However, when the LDO is in full operation (i.e. supplying current to the load) we see that: . This allows us to reduce to the following:

which further reduces the efficiency equation to:

In full operation, it is shown that the efficiency of an LDO is enhanced by minimizing the difference between and . The lower the drop-out specification for a particular LDO, the smaller this differential can be.[6]

It is important to keep thermal considerations in mind when using a low drop-out linear regulator. Having too wide a differential between input and output voltage could lead to large power dissipation. Depending on the package, excessive power dissipation could damage the LDO and/or cause it to go into thermal shutdown.

Quiescent current

Among other important characteristics of a linear regulator is the quiescent current, also known as ground current or supply current, which accounts for the difference, although small, between the input and output currents of the LDO. Quiescent current is current drawn by the LDO in order to control its internal circuitry for proper operation. The series pass element, topologies, and ambient temperature are the primary contributors to quiescent current.[6]

Many applications don't require an LDO to be in full operation all of the time (i.e. supplying current to the load). In this idle state the LDO still draws small amounts of quiescent current in order keep the internal circuitry ready in case the load is enabled. When no current is being supplied to the load, can be found as follows:

In order to minimize power loss while the LDO is idle, quiescent current should be as low as possible. Decreased power consumption allows portable applications to achieve longer battery life. It's also beneficial for enclosed applications that have trouble dissipating heat that may result from inefficient LDOs.

Filtering

In addition to regulating voltage, LDOs can also be used as filters. This is especially useful when a system is utilizing switchers, which introduce a ripple in the output voltage occurring at the switching frequency. Left alone, this ripple has the potential to adversely affect the performance of op-amps,[7] data converters, and RF systems[8] being powered by the switcher. However, any power source, not just switchers, can contain AC elements that may be undesirable for design.

Two specifications that should be considered when using an LDO as a filter are Power Supply Rejection Ratio and Output Noise.

Ripple Rejection

Power supply rejection ratio, or PSRR, refers to the LDO's ability to reject ripple it sees at its input.[9] As part of its regulation, the error amplifier and bandgap attenuate any spikes in the input voltage that deviate from the internal reference to which it is compared.[10] In an ideal LDO, the output voltage would be solely composed of the DC frequency. However, the error amplifier is limited in its ability to gain small spikes at high frequencies. PSRR is expressed as follows:[9]

As an example, an LDO that has a PSRR of 55dB at 1 MHz attenuates a 1mV input ripple at this frequency to just 1.78uV at the output. A 6dB increase in PSRR roughly equates to an increase in attenuation by a factor of 2.

Most LDOs have relatively high PSRR at lower frequencies (10 Hz - 1 kHz). However, a Performance LDO is distinguished in having high PSRR over a broad frequency spectrum (10 Hz - 5 MHz). Having high PSRR over a wide band allows the LDO to reject high-frequency noise like that arising from a switcher. Similar to other specifications, PSRR fluctuates over frequency, temperature, current, output voltage, and the voltage differential.

Output Noise

The noise from the LDO, itself, must also be considered in filter design. Like other electronic devices, LDOs are affected by thermal noise, bipolar shot noise, and flicker noise.[8] Each of these phenomena contribute noise to the output voltage, mostly concentrated over the lower end of the frequency spectrum. In order to properly filter out AC frequencies, an LDO must both reject ripple at the input while introducing minimal noise at the output. Efforts to attenuate ripple from the input voltage could be in vain if a noisy LDO just adds that noise back again at the output. Texas Instruments' TPS7A47 is an example of an LDO with both very low noise and high PSRR over a broad frequency band.[11]

Specifications

LDO is characterized by its drop-out voltage, quiescent current, load regulation, line regulation, maximum current (which is decided by the size of the pass transistor), speed (how fast it can respond as the load varies), voltage variations in the output because of sudden transients in the load current, output capacitor and its equivalent series resistance.[12] Speed is indicated by the rise time of the current at the output as it varies from 0mA load current (no load) to the maximum load current. This is basically decided by the bandwidth of the error amplifier. One should also make sure that there is no positive feedback. So there is a need to do frequency compensation either internally or externally by having only one pole (dominant pole) within its UGB.

See also

Sportspersons Hyslop from Nicolet, usually spends time with pastimes for example martial arts, property developers condominium in singapore singapore and hot rods. Maintains a trip site and has lots to write about after touring Gulf of Porto: Calanche of Piana.

References

43 year old Petroleum Engineer Harry from Deep River, usually spends time with hobbies and interests like renting movies, property developers in singapore new condominium and vehicle racing. Constantly enjoys going to destinations like Camino Real de Tierra Adentro.

External links

- Datasheets

- MCP1702, Microchip, 26 pages, 2010, 2.0 µA quiescent current

- ↑

20 year-old Real Estate Agent Rusty from Saint-Paul, has hobbies and interests which includes monopoly, property developers in singapore and poker. Will soon undertake a contiki trip that may include going to the Lower Valley of the Omo.

My blog: http://www.primaboinca.com/view_profile.php?userid=5889534 - ↑ Template:Cite web

- ↑ LDOs, Low Dropout Regulators, Linear Regulators, CMOS Linear Regulator

- ↑ Template:Cite web

- ↑ http://www.national.com/assets/en/appnotes/f4.pdf Linear and Switching Voltage Regulator Fundamentals

- ↑ 6.0 6.1 Template:Cite web

- ↑ Template:Cite web

- ↑ 8.0 8.1 Template:Cite web

- ↑ 9.0 9.1 Template:Cite web

- ↑ Template:Cite web

- ↑ Template:Cite web

- ↑ Current Efficient, Low Voltage LDO A Thesis by Rincon-Mora